Estrutura física e princípio de funcionamento do MOSFET de potência

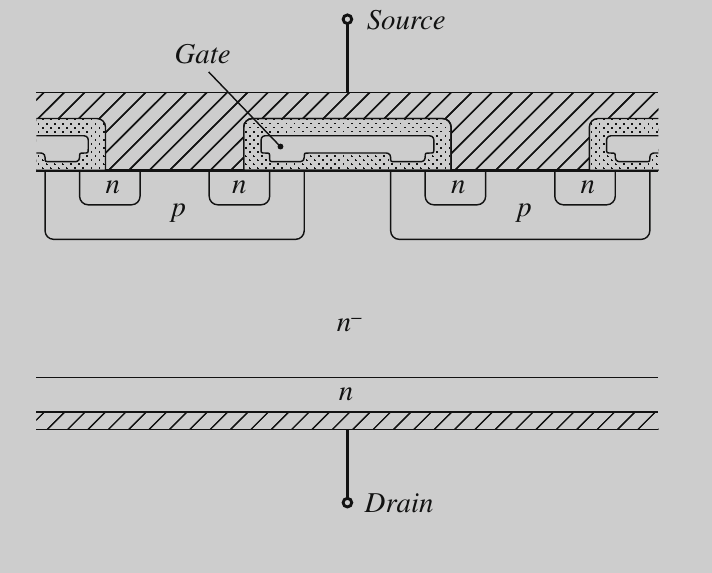

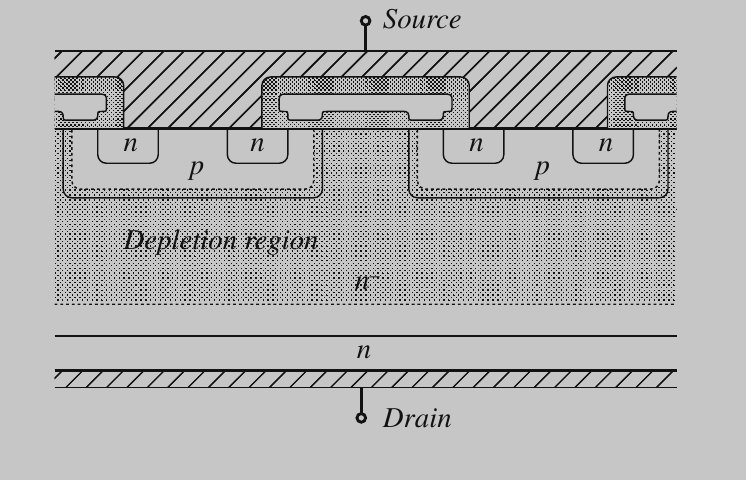

O MOSFET de potência é um dispositivo semicondutor projetado especificamente para operação como chave eletrônica em aplicações de média e alta potência, sendo amplamente utilizado em fontes chaveadas, inversores e conversores DC-DC. Diferentemente dos MOSFETs de sinal pequeno, o MOSFET de potência é constituído por milhares de células MOS conectadas em paralelo sobre o mesmo chip de silício, permitindo condução de correntes elevadas com baixa resistência ôhmica. Essas células são organizadas em uma estrutura conhecida como DMOS vertical, na qual a corrente flui perpendicularmente à superfície do wafer, do dreno para a fonte.

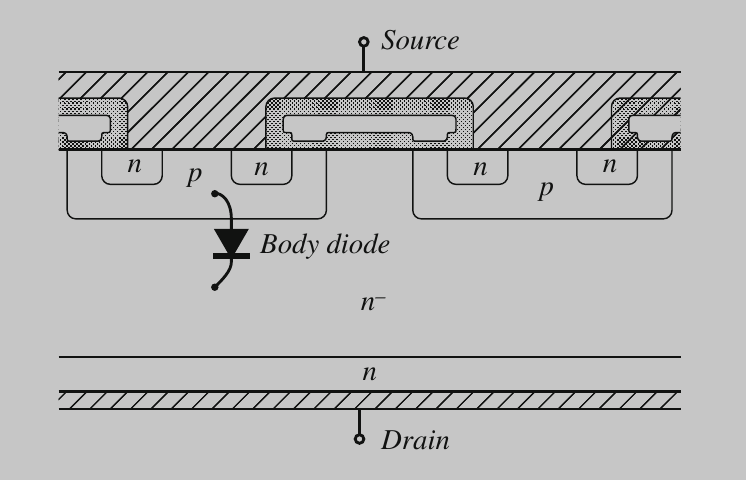

Fisicamente, o dispositivo é composto por uma região n⁻ (drift region) levemente dopada, responsável por suportar a tensão de bloqueio quando o MOSFET está desligado. Acima dessa região encontra-se o substrato p (body), no qual são difundidas regiões n⁺ que formam a fonte. Sobre o substrato p é depositada uma camada isolante de dióxido de silício (SiO₂), e acima dela a porta (gate), tipicamente em polisilício. Essa estrutura cria o capacitor porta-canal, que é o elemento fundamental para o controle do dispositivo.

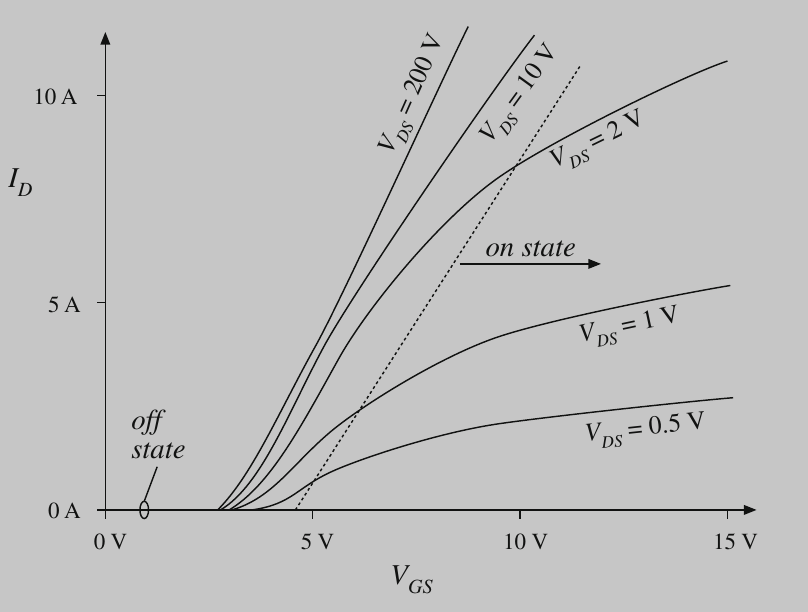

Quando a tensão VGS (gate-source) é inferior à tensão de limiar Vth, não existe canal de condução, e a tensão VDS aparece quase integralmente sobre a região de depleção da junção p–n⁻, mantendo o dispositivo no estado de bloqueio. Ao aplicar uma tensão VGS > Vth, forma-se uma camada de inversão na interface entre o óxido e a região p, criando um canal condutor rico em elétrons. A corrente então flui do dreno para a fonte atravessando sucessivamente a região n⁻, o canal, as regiões n⁺ e os contatos metálicos.

A resistência de condução RDS(on) resulta da soma das resistências internas dessas regiões, sendo fortemente influenciada pela resistividade da região n⁻. À medida que se aumenta a tensão nominal de bloqueio do MOSFET, essa região precisa ser mais espessa e menos dopada, o que eleva significativamente o valor de RDS(on). Essa característica explica por que MOSFETs de alta tensão apresentam maior perda por condução quando comparados a dispositivos de baixa tensão.

Essa descrição estrutural e funcional está detalhada no capítulo 4 do livro Fundamentals of Power Electronics, onde os diagramas de seção transversal mostram claramente os estados de bloqueio, condução e a formação do canal no MOSFET de potência .

Capacitâncias parasitas do MOSFET de potência e seu impacto no chaveamento

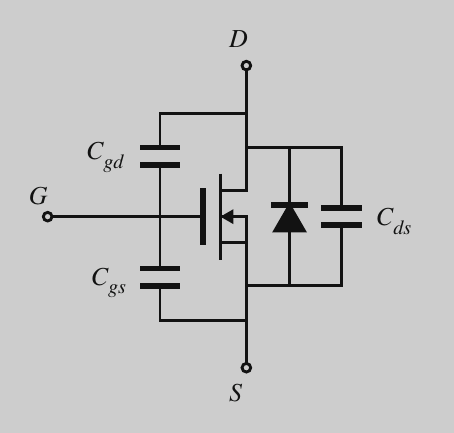

Embora o MOSFET de potência seja conceitualmente um dispositivo controlado por tensão, seu comportamento dinâmico durante o chaveamento é fortemente influenciado pelas capacitâncias parasitas internas, inerentes à sua estrutura física. Essas capacitâncias não são componentes discretos adicionados ao circuito, mas resultam diretamente das junções semicondutoras e da sobreposição geométrica entre os eletrodos do dispositivo. Em aplicações de fontes chaveadas, elas são determinantes para as perdas de comutação, a forma de onda de tensão e corrente, e o esforço exigido do circuito de acionamento da porta.

As três capacitâncias fundamentais são a capacitância porta-fonte (Cgs), a capacitância porta-dreno (Cgd) e a capacitância dreno-fonte (Cds). A capacitância Cgs está associada principalmente à área de sobreposição entre a porta e a região do canal. Ela é aproximadamente linear e representa a carga necessária para criar e sustentar a camada de inversão. Já a capacitância Cgd, frequentemente chamada de capacitância Miller, está relacionada à sobreposição entre a porta e a região do dreno, sendo crítica durante as transições de chaveamento. A capacitância Cds decorre da junção p–n⁻ entre o corpo e a região de deriva, existindo mesmo quando o MOSFET está desligado.

Um ponto essencial, frequentemente negligenciado por iniciantes, é que Cgd e Cds são fortemente não lineares. Essas capacitâncias dependem da tensão aplicada, variando aproximadamente de forma inversamente proporcional à raiz quadrada da tensão dreno-fonte. Esse comportamento pode ser expresso, de forma simplificada, pela relação:

\[

C_{ds}(v_{ds}) = \frac{C_0}{\sqrt{1 + \frac{v_{ds}}{V_0}}}

\]

onde C₀ e V₀ são constantes relacionadas ao processo de fabricação do dispositivo. Essa não linearidade explica por que as perdas de comutação não crescem de forma linear com a tensão de operação e por que o comportamento real do MOSFET difere significativamente de modelos ideais.

Durante o chaveamento, o circuito de gate precisa fornecer ou remover carga dessas capacitâncias. Inicialmente, a corrente de gate é usada para carregar Cgs até que a tensão VGS atinja o limiar e o canal comece a conduzir. Em seguida, ocorre o chamado platô de Miller, no qual a tensão VGS permanece quase constante enquanto a capacitância Cgd é carregada ou descarregada, permitindo a variação de VDS. Nesse intervalo, a velocidade de variação da tensão dreno-fonte é diretamente limitada pela corrente de gate disponível, tornando o projeto do driver de gate um aspecto crítico em fontes chaveadas de alta frequência.

A capacitância Cds tem um impacto direto nas perdas de comutação, pois a energia armazenada nela quando o MOSFET está desligado,

\[

E = \frac{1}{2} C_{ds} V_{DS}^2

\]

é dissipada no momento da ligação do transistor. Essa energia perdida a cada ciclo cresce com a frequência de chaveamento, sendo uma das razões pelas quais, em projetos de alta tensão e alta frequência, a seleção do MOSFET deve considerar não apenas RDS(on), mas também os parâmetros capacitivos e a carga total de gate.

Esses efeitos são descritos de forma clara no modelo equivalente do MOSFET apresentado no capítulo 4 de Fundamentals of Power Electronics, onde as capacitâncias Cgs, Cgd e Cds aparecem explicitamente associadas ao diodo de corpo e às junções internas, permitindo compreender qualitativamente o comportamento dinâmico do dispositivo .

Transistor BJT parasita no MOSFET de potência e riscos durante a comutação

Embora o MOSFET de potência seja classificado como um dispositivo de portadores majoritários, sua estrutura física inevitavelmente dá origem a um transistor bipolar parasita (BJT) embutido no silício. Esse efeito não é acidental nem opcional: ele surge diretamente da disposição das regiões dopadas necessárias para formar o MOSFET vertical. Em um MOSFET canal N típico, a região n⁺ da fonte atua como emissor, a região p do corpo (body) como base, e a região n⁻ de deriva (drift region) como coletor. O resultado é um transistor bipolar NPN parasita, eletricamente presente mesmo que não seja desejado.

Em condições normais de operação, esse transistor parasita permanece desligado porque a base (região p) está curto-circuitada à fonte por meio do contato metálico. Esse curto garante que a junção base-emissor não seja polarizada diretamente, impedindo a condução do BJT. Entretanto, essa condição depende de que a corrente que flui pela região p não gere uma queda de tensão significativa ao longo de sua resistência interna. Em situações de corrente elevada e transições rápidas, essa hipótese pode deixar de ser válida.

Um cenário crítico ocorre durante a recuperação reversa do diodo de corpo, quando o MOSFET estava conduzindo corrente no sentido reverso e é forçado abruptamente a bloquear. Durante esse processo, surgem picos de corrente elevados que atravessam a região p do corpo. Se a queda de tensão nessa região ultrapassar aproximadamente 0,7 V, a junção base-emissor do BJT parasita pode ser polarizada diretamente, ativando o transistor bipolar. Uma vez ativado, o BJT pode entrar em condução regenerativa, caracterizando um fenômeno conhecido como latch-up, que frequentemente resulta na destruição do dispositivo.

Esse mecanismo é particularmente perigoso porque o BJT parasita não é controlado pela porta do MOSFET. Assim, mesmo que o gate esteja em nível baixo, o dispositivo pode permanecer conduzindo corrente elevada até ocorrer falha térmica ou ruptura das junções internas. Em aplicações de fontes chaveadas, esse efeito está diretamente associado a layouts inadequados, alta indutância parasita, comutação agressiva e uso de MOSFETs com diodos de corpo lentos.

Fabricantes modernos mitigam esse problema por meio de otimizações no layout interno do chip, redução da resistência da região p, uso de estruturas trench e melhorias no diodo de corpo. Ainda assim, do ponto de vista do projetista, é fundamental compreender que o MOSFET não é apenas um interruptor ideal, mas um dispositivo com interações internas complexas. Estratégias como controle da taxa de variação de corrente (di/dt), uso de snubbers, escolha adequada do driver de gate e seleção de dispositivos com diodo de corpo rápido são essenciais para evitar a ativação indesejada do BJT parasita.

Essa limitação estrutural e seus riscos são explicitamente discutidos no capítulo 4 de Fundamentals of Power Electronics, onde o transistor bipolar parasita é identificado como um dos principais mecanismos de falha em aplicações de comutação rápida, especialmente durante a recuperação reversa do diodo de corpo .

Diodo de corpo do MOSFET e seu comportamento durante o chaveamento

O diodo de corpo é um elemento intrínseco à estrutura do MOSFET de potência e surge da junção p–n⁻ formada entre a região do corpo (p) e a região de deriva (n⁻). Do ponto de vista elétrico, esse diodo aparece em antiparalelo com o canal do MOSFET, permitindo a condução de corrente quando a tensão dreno-fonte VDS torna-se negativa. Em aplicações de eletrônica de potência, especialmente em conversores com elementos indutivos, essa condução reversa não é apenas comum, mas inevitável.

Durante o funcionamento normal de uma fonte chaveada, quando a corrente do indutor precisa continuar fluindo após o desligamento do transistor, o diodo de corpo passa a conduzir automaticamente. Ele é dimensionado para suportar correntes comparáveis à corrente nominal do MOSFET, o que o torna funcional do ponto de vista de robustez. Entretanto, ao contrário de diodos discretos rápidos ou Schottky, o diodo de corpo de muitos MOSFETs não é otimizado para comutação rápida, apresentando comportamento de recuperação reversa que pode ser severo.

O processo de recuperação reversa ocorre quando o diodo estava conduzindo e, subitamente, passa a ser polarizado inversamente. Nesse instante, cargas armazenadas na região de junção precisam ser removidas antes que o diodo volte a bloquear tensão. Esse fenômeno gera um pico de corrente reversa, cuja amplitude e duração dependem das características do diodo. A energia associada a esse processo é dissipada no MOSFET que força o bloqueio, aumentando as perdas de comutação e elevando o estresse térmico e elétrico do sistema.

Além das perdas, a recuperação reversa do diodo de corpo está intimamente ligada aos problemas discutidos na seção anterior. Os elevados picos de corrente podem provocar quedas de tensão significativas na região p do corpo, criando condições favoráveis à ativação do BJT parasita. Por esse motivo, o diodo de corpo é frequentemente o elo mais crítico do MOSFET em topologias como half-bridge, full-bridge, buck síncrono e boost, onde a condução reversa ocorre a cada ciclo de chaveamento.

Em projetos modernos, duas abordagens são comuns para mitigar esses efeitos. A primeira é a seleção de MOSFETs com diodo de corpo de recuperação rápida, projetados especificamente para suportar correntes elevadas durante a transição reversa. A segunda é o uso de retificação síncrona, onde um segundo MOSFET conduz a corrente reversa através de seu canal, reduzindo drasticamente a queda de tensão e eliminando, na prática, os problemas de recuperação do diodo de corpo. Em ambos os casos, o entendimento profundo do papel desse diodo é essencial para o aumento da eficiência e da confiabilidade da fonte chaveada.

O comportamento do diodo de corpo, sua capacidade de condução e os riscos associados à sua recuperação reversa são descritos de forma detalhada no capítulo 4 de Fundamentals of Power Electronics, onde se destaca que, embora funcionalmente útil, esse diodo pode se tornar um fator limitante em aplicações de alta frequência e alta densidade de potência .